Socialis Series in Social Science ISSN 2583-1585

Singh & Misra, 2024

Volume 7, pp. 17-28

Received: 1st February 2024

Revised: 23rd February 2024 and 28th February 2024

Accepted: 1<sup>st</sup> February 2024

Date of Publication: 15th June 2024

This paper can be cited as: Singh, K. B., Misra, S. C. (2024). Assessment of Success Indicators Associated with

Manufacturing IC Chips In Indian Semiconductor Industry. Socialis Series in Social Science, 07, 17-28,

This work is licensed under the Creative Commons Attribution-NonCommercial 4.0 International License. To view a copy of this license, visit http://creativecommons.org/licenses/by-nc/4.0/ or send a letter to Creative Commons, PO Box 1866, Mountain View, CA 94042, USA.

# ASSESSMENT OF SUCCESS INDICATORS ASSOCIATED WITH MANUFACTURING IC CHIPS IN INDIAN SEMICONDUCTOR INDUSTRY

#### Karam Bharat Singh

Indian Institute of Technology Kanpur, Kalyanpur-208016, Uttar Pradesh, India, The University of Tokyo, Hongo Bunkyo City, Tokyo 113-8654, Japan karambs20@iitk.ac.in

#### Subhas Chandra Misra

Indian Institute of Technology Kanpur, Kalyanpur-208016, Uttar Pradesh, India subhasm@iitk.ac.in

## Abstract

Integrated circuit plays a crucial role in reducing the size, increasing the processing speed, and enhancing the dependability on the electronic devices. Notably, the widespread use of these technologies has led to advancements in various sectors, including the communications, healthcare, and automobile industry. This study rank and identifies the critical success indicators associated with the manufacturing IC chips in the Indian semiconductor industry by employing one sample t-test approach. Based on the existing literature, the study investigates sixteen success indicators associated with the manufacturing IC chips in India. In addition, experts from the semiconductor manufacturing organization have validated these factors concerning the Indian semiconductor industry. The research concludes that "Monitor the Time-to-Market (SI7)", "Enhance Customer Satisfaction (SI13)", "Assess the Yield Rate (SI11)", and "Calculate the Return on Investment (ROI) for Cost (SI5)", are the critical success indicators associated with manufacturing of IC chips, as per the t-test analysis from 152 respondents working in the semiconductor sectors. The findings have multiple implications for businesses and policymaker, and can assist various stakeholders, including global semiconductor companies, domestic manufacturers, and fabless semiconductor firms.

### Keywords

Integrated Circuit (IC), T-Test, Success Indicators, Manufacturing, Cost, Time, Quality

## **1. Introduction**

The integrated circuit (IC) chip has profoundly impacted modern society. The semiconductor industry has consistently experienced an annual doubling in the number of transistors incorporated into IC chips, resulting in the establishment of Moore's Law and propelling the progress of the electronic revolution (MacK, 2011). Moreover, the demand for electronic devices is projected to increase due to the Internet of Things (IoT), distributed artificial intelligence (AI) for edge applications, and the growing popularity of cloud computing (Das & Mao, 2020).

Notably, semiconductor manufacturing industry in developing economy country like India possess the capacity to enhance their GDPs and generate employment opportunities (Pulicherla et al., 2022). The country can enhance its technological prowess, foster innovation, and facilitate information dissemination through chip production. This plan will foster self-sufficiency, decrease dependence on foreign vendors for crucial components, safeguard data sovereignty, and enhance cybersecurity. In addition, the domestic semiconductor manufacturing can enhance the supply chain's resilience, guaranteeing the availability of chips even in the face of global disruptions like the Covid-19 pandemic (Ramani et al., 2022). Moreover, the semiconductor industry possess substantial capacity for employment creation as it cultivates expertise in several fields, and the R&D efforts will propel technological advancements and foster innovative breakthroughs. This can enhance the export of chips, increasing foreign exchange earnings and attracting both domestic and foreign investments.

Furthermore, India has recognized the manufacturing of IC chips as a pivotal industry for enhancing its progress by producing goods for both domestic and global markets. Although company like Apple has primarily been responsible for the country's significant growth in smartphone manufacturing, most of the process involves assembling imported components (Jain et al., 2019). As part of its economic plan to foster a domestic semiconductor manufacturing, the country has emphasized the growth of a domestic electronics supply chain and decreased imports. Furthermore, in 2021, the government initiated the Indian Semiconductor Mission (ISM), allocating a substantial budget of \$10 billion (Saraswat, 2022). The program aims to promote the growth of India's semiconductor and display manufacturing ecosystems. In light of these endeavours and advancements in the semiconductor sector, it is imperative to identify and tackle the various key performance success indicators that will improve the semiconductor ecosystem, which must be studied in detail.

#### **1.1 Motivation**

India can bolster its technological sovereignty and alleviate vulnerabilities associated with supply chain disruptions by establishing a resilient domestic semiconductor manufacturing sector that guarantees self-sufficiency in chip production. Additionally, a resilient semiconductor manufacturing industry supports India's digital transformation aspirations. It gives technological innovation for a strategic advantage in the economic growth and national security. To create a flourishing semiconductor ecosystem in the country, the three dimensions of cost-effectiveness, timeliness, and quality control must be assessed. The semiconductor sector may improve its domestic manufacturing ecology, decision-making process, and technological and economic advancement by conducting these assessments.

## 2. Literature Review

In recent years, the Indian semiconductor fabrication facilities and foreign investment have significantly advanced (Singh et al., 2018). Government initiative program like the "Make in India" and the accompanying policies have encouraged semiconductor investments in the country (Pulicherla et al., 2022). Cooperation between the private sector and academic institutions has promoted R&D advancing technologies. The focus has been on producing fundamental to complex IC chips for consumer electronics, telecommunications, automotive, and other industries.

The success indicators encompass a holistic evaluation of the performance of IC chip manufacturing, encompassing several dimensions. These indicators are utilized by manufacturers to establish objectives, monitor advancements, and consistently enhance their operational procedures. By monitoring and improving these indicators, semiconductor manufacturers can optimize their operations and enhance overall performance. As per the existing literature and the interaction with experts from the semiconductor manufacturing industry, sixteen success indicators from three dimensions viz. cost, time, and quality (Roy et al., 2020), were identified important with manufacturing IC chips and these are mentioned as in Table 1.

| Dimensions | Success Indicators                                         | Descriptions                                                                                                                                                                                                                                    | References                                                                                     |  |  |

|------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|

|            | SI1. Measure the cost per IC                               | The cost of manufacturing each IC chips ensure the cost<br>efficiency. This will set the targets for reducing the cost<br>over time.                                                                                                            | (Guin et al., 2016; Nagapurkar<br>& Das, 2022; Ruberti, 2023)                                  |  |  |

|            | SI2. Track the Material Cost as a Percentage of Total Cost | Tracking the proportion of manufacturing costs<br>attributed to the raw materials, aiming to optimize the<br>raw material usage.                                                                                                                | (Zhu et al., 2021)                                                                             |  |  |

| Cost       | SI3. Monitor the Operating<br>Expense Ratio                | Monitor the operation expenses as a percentage of total costs to ensure the efficiency of resource allocation.                                                                                                                                  | (Khakifirooz et al., 2019; Saif<br>M Khan et al., 2021)                                        |  |  |

|            | SI4. Track the Rework and Scrap Costs                      | Tracking the costs associated with reworking or discarding the defective IC chips, which helps in minimize the expenses.                                                                                                                        | (Hansen et al., 1997; Hickey &<br>Kozlovski, 2020; Tassey et al.,<br>2007; Umeda et al., 2021) |  |  |

|            | SI5. Calculate the Return on<br>Investment (ROI) for Cost  | Calculate the ROI for manufacturing costs. This will<br>help in ensuring that expenditures lead to profitable<br>outcomes.                                                                                                                      | (Hsu et al., 2020; Jamil et al., 2020)                                                         |  |  |

|            | SI6. Measure the Cycle Time                                | Measure the time it takes to manufacture IC chips from<br>start to finish. This will help in setting the targets to<br>reduce cycle time and improve the production efficiency.                                                                 | (Chien et al., 2020; Ishak et al., 2023; Saqlain et al., 2019a)                                |  |  |

|            | SI7. Monitor the Time-to-<br>Market                        | Measure and monitor the time it takes to bring a new IC<br>chip to market for its use. By aiming for shorter<br>timeframes, it will help in staying in competitive market.                                                                      | (C. Park, 2020; Schneider et al., 2022)                                                        |  |  |

| Time       | SI8. Track the Lead Time                                   | Tracking the lead time for raw materials and equipment will ensure in a smooth manufacturing process.                                                                                                                                           | (Chien et al., 2020; Fan et al., 2020; Ishak et al., 2023)                                     |  |  |

|            | SI9. Measure the Equipment<br>Downtime                     | Track the time that manufacturing equipment is non-<br>operational and strive to minimize the downtime for<br>getting the maximize productivity.                                                                                                | (Chung et al., 2023; Fischer et al., 2021; Prasetyo & Veroya, 2020)                            |  |  |

|            | SIIO. Monitor the Time-<br>Based Quality Metrics           | Monitor the time it takes to identify and rectify the defects or errors in the manufacturing process to maintain a high-quality standard chips.                                                                                                 | (Chung et al., 2023; Dreyfus et al., 2022)                                                     |  |  |

|            | SII1. Assess the Yield Rate                                | Assess the percentage of IC chips that meet the given<br>quality standards. These IC chips should be free from<br>defects to ensure a high-quality production.                                                                                  | (Chattopadhyay & Pal, 2017;<br>Lee et al., 2019; Senoner et al.,<br>2021a).                    |  |  |

|            | SI12. Measure the Defect<br>Density                        | Measure the number of defects of IC chips per unit area<br>of the silicon wafer. These will reflect in the quality of<br>the manufacturing process.                                                                                             | (Nakazawa & Kulkarni, 2019;<br>S. H. Park et al., 2018; Saqlain<br>et al., 2019b, 2020)        |  |  |

|            | SI13. Enhance Customer<br>Satisfaction                     | Improve the customer satisfaction with the performance<br>and quality of the manufactured IC chips through various<br>survey and feedback.                                                                                                      | (Chandra Misra et al., 2019;<br>Mousavi et al., 2019; Sansone et<br>al., 2020)                 |  |  |

| Quality    | SI14. Evaluate the Quality<br>Assurance Efficiency         | Measure the efficiency associated with the quality<br>assurance processes during the chip manufacturing, such<br>as conducting multiple testing and inspections. This will<br>ensure the high-quality standards of the chips are<br>maintained. | (Raithatha & Bapat, 2014;<br>Senoner et al., 2021b)                                            |  |  |

|            | S115. Ensure Compliance<br>with Quality Standards          | Check the manufacturing process adheres to quality standards and regulations led down in the manufacturing rule books, aiming for 100% compliance.                                                                                              | (Feng et al., 2023; Pai & Yeh, 2013)                                                           |  |  |

|            | SI16. Track the First Pass<br>Yield                        | Tracking down the percentage of IC chips that pass the<br>quality control check on their first attempt are very<br>crucial for the improvement in efficiency and reduction<br>in reworking of manufacturing processes.                          | (Jiang et al., 2020; Senoner et al., 2021a)                                                    |  |  |

**Table 1:** Success Indicators with their Descriptions

(Source: Authors' Own Illustration)

# 3. Research Approach and Data Collection

#### **3.1. Research Process**

In this study, we used one-sample t-test analysis to compare the responses with an expected level of agreement and evaluate the significance of the success indicators in the manufacturing of IC chips (Alharthi et al., 2017). Moreover, the t-test analysis will check the mean difference with the hypothesized mean of the sample. For the collection of the responses, the Likert scale of rating from 1 to 5, which indicates "Very Low Influence" to "Very High Influence", were utilized to mark the importance of each indicator by the respondents, and the rating scale of 3 which indicates the "Medium Influence" was considered as the hypothesized mean value. Based on the respondent datasets, the variables having mean above 3 was considered significant, and those below 3 were considered not important and insignificant.

Furthermore, the test static (t) against each variable can be calculated as (Kim, 2015):

$$t = \frac{\mu - \mu_o}{\sigma / \sqrt{N}} \tag{1}$$

Where,  $\mu$  is the overall mean from the datasets,  $\mu_0$  is the hypothesized mean,  $\sigma$  is the standard deviation of the dataset, N is the size of the dataset.

After the calculation of t-static, it is required to check the probability of the acceptance/rejection of the hypotheses made of the dataset. Here, the calculated t-static value is compared with the values of t-distribution with (N-1) degree of freedom. Accordingly, the probability can be calculated as follows:

$$p = P(T > t)$$

(Upper tailed) (2)

$$p = P(T < t)$$

(Lower tailed) (3)

Here, lower the p-values, higher is the support to the acceptance of alternate hypothesis and vice-versa. Additionally, the statistically significant level is decided as p < 0.05 under the 95% confidence interval of the difference of the mean.

### **3.2. Data Collection**

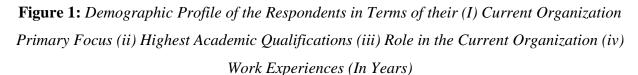

A questionnaire-based study using Likert scale rating from 1 to 5 indicating the influence level of each success indicators was conducted among the broader domain of semiconductor industry executives. The questionnaire was circulated to nearly 500 semiconductor executives through a Google forms (https://forms.gle/Pn72v9cYJkXhFJBy5) via LinkedIn, email, and social networking service. Furthermore, 152 out of nearly 500 executives responded with valid survey responses and their demographic profile can be seen in Figure 1.

(Source: Authors' Own Illustration)

## 4. Result and Discussion

The surveyed dataset from the 152 respondents have been qualified for analysis using a one sample t-test for identifying the critical success indicators for our study. Accordingly, the test value of the study was set at 3 to check the mean of the respondent dataset for the assessment of critical success indicators. Notably, the difference between the mean score from the test value of 3 is the deciding parameter for the ranking of these success indicators. In this study, 14 out of the 16 success indicators were observed as the significant success indicators in the manufacturing of

IC chips in India, while "Track the Rework and Scrap Costs (SI4)" and "Measure the Defect Density (SI12)" were found to be insignificant as per the t-test results in Table 2.

|                       | N   | Mean  | Standard<br>Deviation | Standard<br>Error<br>Mean | Test Value = 3 |                                 |                 |              |                    |                                                 |        |      |

|-----------------------|-----|-------|-----------------------|---------------------------|----------------|---------------------------------|-----------------|--------------|--------------------|-------------------------------------------------|--------|------|

| Success<br>Indicators |     |       |                       |                           | t-static       | Degree<br>of<br>Freedom<br>(df) | Sig. (2-tailed) |              | Mean<br>Difference | 95% Confidence<br>Interval of the<br>Difference |        | Rank |

|                       |     |       |                       |                           |                |                                 | Actual<br>value | Round<br>off | Difference         | Lower                                           | Upper  |      |

| SI1                   | 152 | 4.026 | 0.861                 | 0.070                     | 14.699         | 151                             | 6.310E-31       | 0.000        | 1.026              | 1.164                                           | 0.888  | 9    |

| SI2                   | 152 | 4.021 | 0.805                 | 0.065                     | 15.639         | 151                             | 2.165E-33       | 0.000        | 1.021              | 1.150                                           | 0.892  | 10   |

| SI3                   | 152 | 4.110 | 0.862                 | 0.070                     | 15.873         | 151                             | 5.361E-34       | 0.000        | 1.110              | 1.249                                           | 0.972  | 5    |

| SI4                   | 152 | 3.117 | 0.916                 | 0.074                     | 1.578          | 151                             | 1.167E-01       | 0.117        | 0.117              | 0.264                                           | -0.030 | IS   |

| SI5                   | 152 | 4.359 | 0.675                 | 0.055                     | 24.812         | 151                             | 3.843E-55       | 0.000        | 1.359              | 1.467                                           | 1.250  | 4    |

| <i>SI6</i>            | 152 | 3.903 | 0.865                 | 0.070                     | 12.873         | 151                             | 4.600E-26       | 0.000        | 0.903              | 1.042                                           | 0.765  | 11   |

| SI7                   | 152 | 4.490 | 0.564                 | 0.046                     | 32.577         | 151                             | 3.485E-70       | 0.000        | 1.490              | 1.580                                           | 1.399  | 1    |

| SI8                   | 152 | 4.041 | 0.821                 | 0.067                     | 15.640         | 151                             | 2.161E-33       | 0.000        | 1.041              | 1.173                                           | 0.910  | 7    |

| SI9                   | 152 | 3.641 | 1.092                 | 0.089                     | 7.238          | 151                             | 2.147E-11       | 0.000        | 0.641              | 0.816                                           | 0.466  | 14   |

| SI10                  | 152 | 3.717 | 1.024                 | 0.083                     | 8.639          | 151                             | 7.545E-15       | 0.000        | 0.717              | 0.881                                           | 0.553  | 12   |

| SI11                  | 152 | 4.366 | 0.569                 | 0.046                     | 29.609         | 151                             | 9.170E-65       | 0.000        | 1.366              | 1.457                                           | 1.274  | 3    |

| SI12                  | 152 | 3.262 | 1.353                 | 0.110                     | 2.388          | 151                             | 1.819E-02       | 0.018        | 0.262              | 0.479                                           | 0.045  | IS   |

| SI13                  | 152 | 4.393 | 0.643                 | 0.052                     | 26.692         | 151                             | 4.772E-59       | 0.000        | 1.393              | 1.496                                           | 1.290  | 2    |

| SI14                  | 152 | 3.703 | 1.050                 | 0.085                     | 8.260          | 151                             | 6.829E-14       | 0.000        | 0.703              | 0.872                                           | 0.535  | 13   |

| SI15                  | 152 | 4.028 | 0.826                 | 0.067                     | 15.344         | 151                             | 1.277E-32       | 0.000        | 1.028              | 1.160                                           | 0.895  | 8    |

| SI16                  | 152 | 4.097 | 0.779                 | 0.063                     | 17.365         | 151                             | 8.094E-38       | 0.000        | 1.097              | 1.221                                           | 0.972  | 6    |

Table 2. One Sample T-Test Statistics

(Source: Authors' Own Illustration)

Furthermore, to identify the most influential attributes, the 80-20 rule from the Pareto principle helps identify a system's most significant or the critical factors (Sanders, 1987). This principle implies that 20% of system elements possess the highest level of importance. In this study, the critical success indicators which are found highly significant are: "Monitor the Time-to-Market (SI7)", "Enhance Customer Satisfaction (SI13)", 'Assess the Yield Rate (SI11)", and "Calculate the Return on Investment (ROI) for Cost (SI5)", as per the Pareto principle.

Notably, the growing demand for the electronic devices in various sectors and the nation's dedication to the self-reliance and progress have led to a thriving semiconductor ecosystem. Moreover, the alignment of the semiconductor market demand and domestic manufacturing capability positively impacts the economic growth, and India's standing in the global semiconductor industry. Additionally, the government has created an enabling environment for the growth and success of domestic manufacturers and the foreign semiconductor investors by implementing a comprehensive strategy and policy like the Indian semiconductor mission (ISM). Additionally, these strategies encompass the formulation of various policies, the provision of financial incentives, large investment in R&D, developing state of the art infrastructures, enhancing the technical skills, and establishing a strong strategic collaboration.

Furthermore, India's ability to build a robust presence in the semiconductor ecosystem and effectively meet the market demands, stimulate novel innovations, and thrive in the competitive landscape of manufacturing IC chips will be contingent upon its sustained investment in cutting-edge infrastructure.

## **5.** Conclusion

This study aimed to identify and ranked the success indicators that promote the manufacturing of IC chips within Indian semiconductor organization. The study thoroughly reviewed relevant academic research to ascertain the success indicators linked to the semiconductor manufacturing process. The identification and validations of these success indicators were validated through in-depth conversations with the engineers and scientists working in the semiconductor organizations. After identifying sixteen success indicators, a general study was conducted among the broader domain of semiconductor industry executives and the questionnaire using the Likert scale was sent through the Google forms. Notably, 152 executives responded with a valid survey response, and one sample t-test analysis was utilized to assess the underlying components and to identify the critical success indicators. The findings of the study indicate that certain success indicators, specifically labelled as "Monitor the Time-to-Market (SI7)", "Enhance Customer Satisfaction (SI13)", "Assess the Yield Rate (SI11)", and "Calculate the Return on Investment (ROI) for Cost (SI5)", were consistently recognized as critical success indicators associated with an effective manufacturing of IC chips in India. These success indicators were deemed essential and required consideration to succeed in the fabrication process of IC chips in India.

This study has the potential to offer significant insights for several stakeholders, such as global semiconductor firms, domestic manufacturers, fabless semiconductor enterprises, and policymakers. It can assist individuals in formulating effective ways to maximize the usage of their considerable investments. The implications of these findings hold great importance for organizations and academia seeking to cultivate a collaborative atmosphere and leverage the benefits of a collective strategy.

### REFERENCES

- Alharthi, A., Alassafi, M. O., Walters, R. J., & Wills, G. B. (2017). An exploratory study for investigating the critical success factors for cloud migration in the Saudi Arabian higher education context. *Telematics and Informatics*, 34(2), 664–678. <u>https://doi.org/10.1016/J.TELE.2016.10.008</u>

- Chandra Misra, S., Balmukund Rahi, S., Bisui, S., & Singh, A. (2019). Factors Influencing the Success of Cloud Adoption in the Semiconductor Industry. *Software Quality Professional*, 21(2), 38–51. https://www.researchgate.net/publication/334895496

- Chattopadhyay, S., & Pal, S. (2017). Availability of Infrastructure Facilities in India: Prospects and Challenges. *Availability of Infrastructure Facilities in India: Prospects and Challenges*, 143–163.

- Chien, C. F., Lin, Y. S., & Lin, S. K. (2020). Deep reinforcement learning for selecting demand forecast models to empower Industry 3.5 and an empirical study for a semiconductor component distributor. *International Journal of Production Research*, 58(9), 2784– 2804. https://doi.org/10.1080/00207543.2020.1733125

- Chung, E., Park, K., & Kang, P. (2023). Fault classification and timing prediction based on shipment inspection data and maintenance reports for semiconductor manufacturing equipment. *Computers & Industrial Engineering*, 176, 108972. https://doi.org/10.1016/J.CIE.2022.108972

- Das, S., & Mao, E. (2020). The global energy footprint of information and communication technology electronics in connected Internet-of-Things devices. *Sustainable Energy, Grids and Networks*, 24, 100408. <u>https://doi.org/10.1016/J.SEGAN.2020.100408</u>

- Dreyfus, P. A., Psarommatis, F., May, G., & Kiritsis, D. (2022). Virtual metrology as an approach for product quality estimation in Industry 4.0: a systematic review and integrative conceptual framework. *International Journal of Production Research*, 60(2), 742–765. <u>https://doi.org/10.1080/00207543.2021.1976433</u>

- Fan, S. K. S., Hsu, C. Y., Tsai, D. M., He, F., & Cheng, C. C. (2020). Data-Driven Approach for Fault Detection and Diagnostic in Semiconductor Manufacturing. *IEEE Transactions* on Automation Science and Engineering, 17(4), 1925–1936. <u>https://doi.org/10.1109/TASE.2020.2983061</u>

- Feng, N., Zhang, Y., Ren, B., Dou, R., & Li, M. (2023). How Industrial Internet Platforms guide high-quality information sharing for semiconductor manufacturing? An evolutionary

game model. *Computers & Industrial Engineering*, *183*, 109449. https://doi.org/10.1016/J.CIE.2023.109449

- Fischer, D., Moder, P., & Ehm, H. (2021). Investigation of Predictive Maintenance for Semiconductor Manufacturing and its Impacts on the Supply Chain. *Proceedings of the IEEE International Conference on Industrial Technology*, 2021-March, 1409– 1416. https://doi.org/10.1109/ICIT46573.2021.9453481

- Guin, U., Forte, D., & Tehranipoor, M. (2016). Design of accurate low-cost on-chip structures for protecting integrated circuits against recycling. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, 24(4), 1233–1246. <u>https://doi.org/10.1109/TVLSI.2015.2466551</u>

- Hansen, M. H., Nair, V. N., & Friedman, D. J. (1997). Monitoring wafer map data from integrated circuit fabrication processes for spatially clustered defects. *Technometrics*, 39(3), 241–253. <u>https://doi.org/10.1080/00401706.1997.10485116</u>

- Hickey, P., & Kozlovski, E. (2020). E-strategies for aftermarket facilitation in the global semiconductor manufacturing industry. *Journal of Enterprise Information Management*, 33(3), 457–481. <u>https://doi.org/10.1108/JEIM-05-2019-</u> 0124/FULL/XML

- Hsu, P. Y., Yeh, I. W., Tseng, C. H., & Lee, S. J. (2020). A Boosting Regression-Based Method to Evaluate the Vital Essence in Semiconductor Industry Performance. *IEEE Access*, 8, 156208–156218. <u>https://doi.org/10.1109/ACCESS.2020.3019332</u>

- Ishak, S., Shaharudin, M. R., Salim, N. A. M., Zainoddin, A. I., & Deng, Z. (2023). The Effect of Supply Chain Adaptive Strategies during the COVID-19 Pandemic on Firm Performance in Malaysia's Semiconductor Industries. *Global Journal of Flexible Systems Management*, 24(3), 439–458. <u>https://doi.org/10.1007/S40171-023-00347-Y/TABLES/7</u>

- Jain, V., Chawla, C., Arya, S., Agarwal, R., & Agarwal, M. (2019). An Empirical Study of Product Design for New Product Development with Special Reference to Indian Mobile Industry. *TEST Engineering & Management*, 81, 1241–1254. <u>https://www.researchgate.net/publication/337732542</u>

- Jamil, J. M., Nizal, I., Shaharanee, M., Faizal, A., Fazil, M., & Sheng, A. J. (2020). Framework to Reduce Cost Scrapping and Cost of Assemble Test Capacity in Semiconductor

Integrated Circuit Manufacturing. *Framework*, 62(07). https://www.researchgate.net/publication/344082931

- Jiang, D., Lin, W., & Raghavan, N. (2020). A novel framework for semiconductor manufacturing final test yield classification using machine learning techniques. *IEEE Access*, 8, 197885–197895. <u>https://doi.org/10.1109/ACCESS.2020.3034680</u>

- Khakifirooz, M., Fathi, M., & Wu, K. (2019). Development of Smart Semiconductor Manufacturing: Operations Research and Data Science Perspectives. *IEEE Access*, 7, 108419–108430. <u>https://doi.org/10.1109/ACCESS.2019.2933167</u>

- Kim, T. K. (2015). T test as a parametric statistic. *Korean Journal of Anesthesiology*, 68(6), 540– 546. <u>https://doi.org/10.4097/KJAE.2015.68.6.540</u>

- Lee, D. H., Yang, J. K., Lee, C. H., & Kim, K. J. (2019). A data-driven approach to selection of critical process steps in the semiconductor manufacturing process considering missing and imbalanced data. *Journal of Manufacturing Systems*, 52, 146–156. https://doi.org/10.1016/J.JMSY.2019.07.001

- MacK, C. A. (2011). Fifty years of Moore's law. IEEE Transactions on Semiconductor Manufacturing, 24(2), 202–207. <u>https://doi.org/10.1109/TSM.2010.2096437</u>

- Mousavi, B. A., Azzouz, R., & Heavey, C. (2019). MATHEMATICAL MODELLING OF PRODUCTS ALLOCATION TO CUSTOMERS FOR SEMICONDUCTOR SUPPLY CHAIN. *Procedia Manufacturing*, 38, 1042–1049. https://doi.org/10.1016/J.PROMFG.2020.01.190

- Nagapurkar, P., & Das, S. (2022). Economic and embodied energy analysis of integrated circuit manufacturing processes. *Sustainable Computing: Informatics and Systems*, 35, 100771. <u>https://doi.org/10.1016/J.SUSCOM.2022.100771</u>

- Nakazawa, T., & Kulkarni, D. V. (2019). Anomaly detection and segmentation for wafer defect patterns using deep Convolutional Encoder-Decoder Neural Network Architectures in Semiconductor Manufacturing. *IEEE Transactions on Semiconductor Manufacturing*, 32(2), 250–256. <u>https://doi.org/10.1109/TSM.2019.2897690</u>

- Pai, F. Y., & Yeh, T. M. (2013). Effective implementation for introducing ISO/TS 16949 in semiconductor manufacturing industries. *Total Quality Management & Business Excellence*, 24(3–4), 462–478. <u>https://doi.org/10.1080/14783363.2012.728854</u>

- Park, C. (2020). Market entry strategies in a high-tech successive generations market: a case study of three semiconductor firms with different entry modes. *Journal of Business* and Industrial Marketing, 35(11), 1751–1766. <u>https://doi.org/10.1108/JBIM-08-2019-0354/FULL/XML</u>

- Park, S. H., Kim, S., & Baek, J. G. (2018). Kernel-Density-Based Particle Defect Management for Semiconductor Manufacturing Facilities. *Applied Sciences 2018, Vol. 8, Page 224*, 8(2), 224. <u>https://doi.org/10.3390/APP8020224</u>

- Prasetyo, Y. T., & Veroya, F. C. (2020). An Application of Overall Equipment Effectiveness (OEE) for Minimizing the Bottleneck Process in Semiconductor Industry. 2020 IEEE 7th International Conference on Industrial Engineering and Applications, ICIEA 2020, 345–349. https://doi.org/10.1109/ICIEA49774.2020.9101925

- Pulicherla, K. K., Adapa, V., Ghosh, M., & Ingle, P. (2022). Current efforts on sustainable green growth in the manufacturing sector to complement "make in India" for making "selfreliant India." *Environmental Research*, 206, 112263. <u>https://doi.org/10.1016/J.ENVRES.2021.112263</u>

- Raithatha, M., & Bapat, V. (2014). Accounting Standards Compliance: Comparison between Manufacturing and Service Sector Companies from India. *International Journal of Economics and Finance*, 6(9). <u>https://doi.org/10.5539/ijef.v6n9p158</u>